ALU, CU : 산술논리장치와 제어장치로 구성

중앙처리장치는 비교, 판단, 연산을 담당하는 산술논리장치(Arithmetic Logic Unit)와 명령어의 해석과 실행을 담당하는 제어장치(Control Unit)로 구성된다.

산술논리장치(ALU)는 각종 덧셈을 수행하고 결과를 수행하는 가산기(adder)와 산술과 논리연산의 결과를 일시적으로 기억하는 레지스터인 누산기(accumulater), 중앙처리장치에 있는 일종의 임시 기억장치인 레지스터(Register) 등으로 구성되어 있다.

제어장치(CU)는 프로그램의 수행 순서를 제어하는 프로그램 계수기(Program Counter), 현재 수행중인 명령어의 내용을 임시 기억하는 명령 레지스터(Instruction register), 명령 레지스터에 수록된 명령을 해독하여 수행될 장치에 제어신호를 보내는 명령해독기(Instruction Decoder)로 이루어져 있다.

[Intel CPU의 역사]

Micro Processor

i4004

i4040

i8008

i8080

i8085

i8086

i8088

i80186

i80286

Real Mode / Protected Mode

i80386

i80386SX

보조프로세서

(8087, 80287, 80387)

i80486

(한번의 클럭으로 1개의 명령어 처리 가능해짐)

ODP(Over Drive Processor)

Pentium(Pent + Intel + UM)

P54C

Pentium Pro(P6)

P55C(Pentium MMX)

Pentium II

펜티엄II 종류

Pentium III

Pentium 4 - Pentium 4 HT - Core2 Duo -

Core2 Quad(헥사코어-옥타코어) - i Series(3, 5, 7)...

[Cache Memory]

CPU의 등급과 가격을 구분 짓는 중요한 지표...

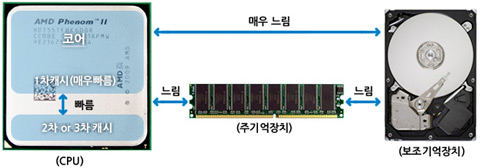

클럭 속도와 코어의 수 외에도, CPU의 성능을 가늠할 수 있는 또 하나의 기준은 CPU 안에 들어 있는 캐시 메모리(cache memory)의 용량이다.

‘캐시’라 줄여 부르는데, CPU 내부의 임시 저장공간으로서 CPU가 데이터를 처리할 때 자주 사용하는 데이터를 임시 보관하는 곳이다.

이 캐시 메모리의 용량이 작으면 CPU에 비해 동작 속도가 훨씬 느린 주 기억장치(RAM, 메모리)나 보조 기억 장치(하드디스크, CD-ROM 등)로부터 직접 데이터를 불러들이는 빈도가 높아지는데, 이런 경우 컴퓨터의 전반적인 처리 속도가 크게 저하된다.

결론적으로 CPU의 캐시 메모리는 크면 클수록 성능 향상에 유리하다.

L1 캐시(Level 1)

CPU코어 안에내장된 캐시 메모리

명령캐시와 데이터 캐시로 나눔

L2 캐시(Level 2)

L1캐시와 메인메모리 사이의 캐시 메모리

CPU 처리 데이터를 메인 메모리(RAM)에서 미리 가져와

저장 해 놓음, 속도향상 효과

L3 캐시(Level 3)

L2캐시의 완충역할, L2가 빠름, 메인 메모리와의 속도 차 보완

CPU의 성능을 결정하는 요인

아키텍처 : 제조공정 (Tr과 Tr을 연결하는 선의 굵기)

[Sandy Bridge 32nm, Ivy Bridge 22nm]

L2 캐시(Cache) : 용량이 클수록 좋음

L3 캐시(Cache) : 용량이 클수록 좋음(특정 CPU에만 장착)

클럭(Clock)속도 : 작동 클럭 속도가 빠를 수록 좋음

FSB(Front Side Bus) : 시스템버스(FSB)가 빠를 수록 좋음

[FSB = CPU - North Bridge (or RAM) BUS]

소켓(Socket) : CPU 핀 수가 많을 수록 좋음

낮은 전압으로 작동되는 CPU

+ 개별 실습과제 H/W CPU 정보검색 +

(스스로 정보검색 문제해결...)

1. 나노(nm) 단위의 의미?

2. Intel CPU 각 세대별 구분과 CPU 코드명은?

3. Sandy Bridge ? 세대 / Ivy Bridge ? 세대

4. 현재 가장 최근에 나온 Intel CPU 코드명과 세대는?

[CPU Over Clocking]

CPU를 정해진 규격의 Clock보다 높은 Clock으로

설정하여 사용하는 것.

모든 CPU가 Over Clocking이 가능한 것은 아님.

메인보드가 Over Clocking을 지원해야 함.

최근 메인보드는 Auto Over Clocking 기능이 내장.

Intel(Turbo Boost), AMD(Turbo Core) 기술 내장.

클럭(Clock)

컴퓨터 뿐만 아니라 관련 장치들은 모두 주기적인 전자신호로 데이터를 주고 받고 처리한다.

이 전자신호의 빠르기를 일컫는 말로 클럭이라는 표현을 쓰며, 단위는 Hz 를 사용한다.

1Hz 라는 것은 1초에 전자신호의 주기가 1번 바뀌는 것으로, MHz는 1초에 1,000,000번, GHz 라는 것은 1초에 약 1,000,000,000번 움직임을 의미한다.

CPU의 속도를 나타내는 대표적인 단위는 ‘클럭(clock)’인데, 이는 1초당 CPU 내부에서 몇 단계의 작업이 처리되는 지를 측정해 이를 주파수 단위인 ‘Hz(헤르츠)’로 나타낸 것이다.

따라서, 이 클럭 수치가 높을수록 빠른 성능의 CPU라고 할 수 있다. 참고로, 1971년에 등장한 세계 최초의 컴퓨터 CPU인 ‘인텔(Intel) 4004’의 최대 동작 클럭은 740KHz(74만Hz)였으며, 2010년 현재 판매 중인 CPU인 ‘인텔 코어(Core) i7 960’의 동작 클럭은 3.2GHz(32억Hz)에 달한다.

과거에는 이러한 클럭 속도가 CPU의 성능을 나타내는 절대적인 기준이었지만, 최근에는 하나의 CPU에 2개 이상의 코어(Core)를 집어넣은 다중 코어(멀티 코어, Multi Core) CPU가 등장하여, CPU의 성능을 나타내는 또 하나의 기준이 되고 있다.

컴퓨터 CPU에서 코어란 CPU에 내장된 처리회로의 핵심 부분으로서, 예전에는 1개의 CPU 당 1개의 코어(단일 코어: Single Core)만을 가지고 있는 것이 당연했다. 1990년대 후반과 2000년대 초반을 즈음하여, 산업용/전문가용 컴퓨터를 위한 다중 코어 CPU가 출시된 적은 있었으나 특수한 환경에서만 사용되어 컴퓨터 시장에 미치는 영향은 극히 미미했다. 하지만 2005년, 2개의 코어를 갖춘 듀얼 코어(Dual Core) CPU인 인텔의 ‘펜티엄(Pentium) D’와 AMD의 ‘애슬론(Athlon)64 X2’가 등장하면서 다중 코어 CPU가 점차 대중화되기 시작했다.

2007년에는 4개의 코어를 갖춘 쿼드 코어(Quad Core) CPU인 인텔의 ‘코어2 쿼드(Core2 Quad)가 등장했으며, 2008년에는 듀얼 코어와 쿼드 코어 사이의 틈새시장을 노린 코어 3개짜리 트리플 코어(Triple Core) CPU인 AMD의 페넘(Phenom) X3도 출시되어 사용자들의 관심을 받았다. 또한, 2010년에는 코어를 6개나 내장한 헥사 코어(Hexa Core) CPU, 인텔의 ‘코어 i7 980X 익스트림 에디션(Extreme Edition)’도 출시된 바 있다.

Over Clocking 문제점

시스템 불안정, 다운 발생

하드 디스크 손상

CPU의 수명 단축

튜닝 후 발생되는 문제는 무상지원이 불가능

시스템 버스 (System Bus Speed)

CPU - 메모리 컨트롤러 - 메모리

[IntelCPU의 동작클럭 속도 / L2 Cache / FSB 비교]

[Intel Celeron CPU]

[CPU 온도]

[LGA Intel CPU & Cooler 분해/조립]

'■■▶PC 정비◀' 카테고리의 다른 글

| 4=PC 정비(RAM, 주기억장치) (0) | 2010.10.11 |

|---|---|

| 3=PC 정비(Intel, AMD CPU Socket 정리 / Intel CPU 1155 Socket) (0) | 2010.10.09 |

| 2=PC 정비(Main Board Slot & 내부 구조와 명칭) (0) | 2010.10.08 |

| 2=PC 정비(Main Board Back Panel & Front Panel, Power Supply) (0) | 2010.10.07 |

| 1=PC 정비(Power Supply Interface) & EMI, PFC, 80 Plus Logo (0) | 2010.10.06 |